Evaluation of split-radix IFFT algorithms in hardware

Main Article Content

Abstract

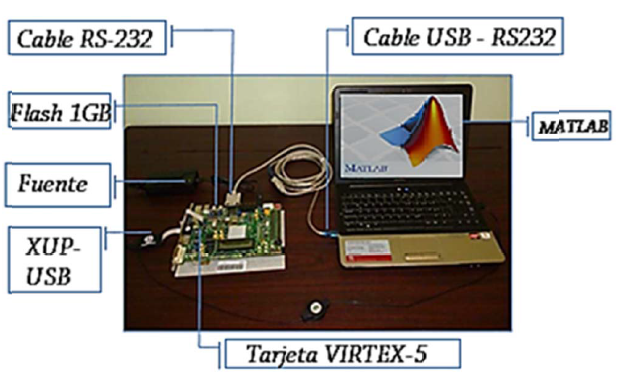

The present work focuses on a hardware-based approach to experimentally identify the best-performing algorithm for calculating the IFFT of an OFDM symbol of the ISDBT-b standard. To accomplish this goal, symmetric and asymmetric Split-radix algorithms are described, and their entire hardware implementation is developed. The test results incorporate other algorithms known as radix-2 lite, radix-2, radix-4, and pipelined. The comparative evaluation of the performance of the algorithms was performed considering the following parameters: Signal to Quantize Noise Ratio (SQNR), processing time, and the amount of resources used by the Virtex-5 XUPV5-LX110T card. The analysis shows that the algorithm that presents the best performance depends on the parameter analyzed.

Downloads

Article Details

This work is licensed under a Creative Commons Attribution 4.0 International License.

Authors who publish in this journal agree to the following terms: Authors retain the copyright and guarantee the journal the right to be the first publication of the work, as well as, licensed under a Creative Commons Attribution License that allows others share the work with an acknowledgment of the authorship of the work and the initial publication in this journal. Authors may separately establish additional agreements for the non-exclusive distribution of the version of the work published in the journal (for example, placing it in an institutional repository or publishing it in a book), with acknowledgment of its initial publication in this journal. Authors are allowed and encouraged to disseminate their work electronically (for example, in institutional repositories or on their own website) before and during the submission process, as it may lead to productive exchanges as well as further citation earliest and oldest of published works.

How to Cite

References

[2] P. Rossi Sancho, “Análisis De Las Arquitecturas De La Transformada Rápida De Fourier”, Sevilla: Universidad de Sevilla, 2016, pp. 6-19. [Online]. Available: http://bibing.us.es/proyectos/abreproy/11014/fichero/Volumen+1%252F2.-+Calculo+eficiente+de+la+transformada+de+Fourier.pdf [Accessed: 24- Feb- 2016].

[3] Freescale Semiconductor, “Software Optimization of FFTs and IFFTs Using the SC3850 core”, 2010. [Online]. Available: http://cache.freescale.com/files/dsp/doc/app_note/AN3666.pdf [Accessed: 24- Feb- 2016].

[4] P. Duhamel, H. Hollman, “Split-radix FFT algorithm”, Electronic Letters, vol. 20, no. 1, 1984, pp. 14 – 16.

[5] P. Duhamel, H. Hollman, “Implementation of Split-radix FFT algorithms for Complex, Real and Real symmetric data”, IEEE Transactions on Acoustics, Speech, and Digital Signal Processing, vol. ASSP-34, no. 2, 1986, pp. 285 – 295.

[6] E. İnceöz, E. Çavuş, “FPGA Implementation of Variable-Length Split-Radix FFT Algorithm”, International Journal of Engineering Science and Computing, vol. 7, no. 7, 2017, pp. 13977-13980.

[7] A. Das, A. Mankar, N. Prasad, K. K. Mahapatra, A. S. Swain, “Efficient VLSI architectures of split radix FFT using NEDA,” International Journal of Engineering Science and Computing, vol. 3, no. 1, pp. 264 271, Mar. 2013.

[8] Zhuo Qian et al., “Low-Power Split-Radix FFT Processors Using Radix-2 Butterfly Units,” IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol 24, no. 9, pp. 3008-3012, Sep. 2016.

[9] S. Hassan et al, “Implementation of Pipelined FFT Processor on FPGA Microchip Proposed for Mechanical Applications”, Journal of Mechanical Engineering, Vol SI 2, p. 145-156, Jan. 2017.

[10] C. Bran, "Sistemas Embebidos: Diseño de Maquinas de Estado Finito con VHDL", 2015. [Online]. Available: http://systemonfpga.blogspot.com/2015/04/diseno-de-maquinas-de-estado-finito-con.html. [Accessed: 24- Feb- 2016].

[11] P. Correa, “Implementación en una FPGA de la Transformada Inversa de Fourier para la Transmisión de la Señal OFDM del Sistema de Televisión Digital Terrrestre ISDBTb”, Proyecto fin de carrera, EPN, 2016.

[12] B. Belzuzarri, “Herramienta En Punto Fijo”, 2013. [Online]. Available: http://bibing.us.es/proyectos/abreproy/11177/fichero/Capitulo_1.pdf [Accessed: 24- Feb- 2016].