Evaluación en hardware de los algoritmos split-radix para la implementación de la IFFT

Contenido principal del artículo

Resumen

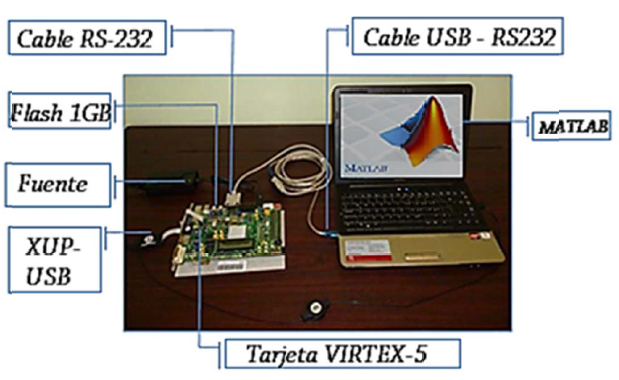

El objetivo de este trabajo fue identificar experimentalmente en hardware, el algoritmo que presentó el mejor desempeño para el cálculo de la IFFT de un símbolo OFDM del estándar ISDBT-b. Para esto, se describen los algoritmos Split-radix simétrico y asimétrico y se desarrolla toda su implementación en hardware. Los resultados de las pruebas incorporan también otros algoritmos conocidos como radix-2 lite, radix-2, radix-4 y pipelined. La evaluación comparativa del rendimiento de los algoritmos se realizó considerando los siguientes parámetros: la Relación Señal a Ruido de Cuantificación (SQNR), tiempo de procesamiento y la cantidad de recursos utilizados de la tarjeta Virtex-5 XUPV5-LX110T. Del análisis se obtiene que el algoritmo que presenta el mejor desempeño depende del parámetro analizado.

##plugins.themes.bootstrap3.displayStats.downloads##

##plugins.themes.bootstrap3.displayStats.noStats##

Detalles del artículo

Número

Sección

ARTÍCULOS TÉCNICOS

Esta obra está bajo una licencia internacional Creative Commons Atribución 4.0.

Los autores que publican en esta revista están de acuerdo con los siguientes términos: Los autores conservan los derechos de autor y garantizan a la revista el derecho de ser la primera publicación del trabajo al igual que licenciado bajo una Creative Commons Attribution License que permite a otros compartir el trabajo con un reconocimiento de la autoría del trabajo y la publicación inicial en esta revista. Los autores pueden establecer por separado acuerdos adicionales para la distribución no exclusiva de la versión de la obra publicada en la revista (por ejemplo, situarlo en un repositorio institucional o publicarlo en un libro), con un reconocimiento de su publicación inicial en esta revista. Se permite y se anima a los autores a difundir sus trabajos electrónicamente (por ejemplo, en repositorios institucionales o en su propio sitio web) antes y durante el proceso de envío, ya que puede dar lugar a intercambios productivos, así como a una citación más temprana y mayor de los trabajos publicados.Cómo citar

Evaluación en hardware de los algoritmos split-radix para la implementación de la IFFT. (2018). MASKAY, 8(1), 20-26. https://doi.org/10.24133/maskay.v8i1.564